# **Autonomic Visualisation**

David Chisnall

A thesis submitted to the University of Wales in candidature for the degree of Philosophiae Doctor

Department of Computer Science University of Wales, Swansea

January 10, 2008

# Declaration

This work has not been previously accepted in substance for any degree and is not being concurrently submitted in candidature for any degree.

Signed Marin (candidate)

Date .....January.10, 2008.....

# **Statement 1**

This thesis is the result of my own investigations, except where otherwise stated. Other sources are acknowledged by footnotes giving explicit references. A bibliography is appended.

Signed (candidate) .....January 10, 2008 Date

# **Statement 2**

I hereby give my consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.

Mor 5 MMM Signed . . . . . . . . . . . . . . . . (candidate)

Date

.....January.10, 2008.....

## Summary

This thesis introduces the concept of autonomic visualisation, where principles of autonomic systems are brought to the field of visualisation infrastructure. Problems in visualisation have a specific set of requirements which are not always met by existing systems.

The first half of this thesis explores a specific problem for large scale visualisation; that of data management. Visualisation algorithms have somewhat different requirements to other external memory problems, due to the fact that they often require access to all, or a large subset, of the data in a way that is highly dependent on the view. This thesis proposes a knowledge-based approach to pre-fetching in this context, and presents evidence that such an approach yields good performance.

The knowledge based approach is incorporated into a five-layer model, which provides a systematic way of categorising and designing out-of-core, or external memory, systems. This model is demonstrated with two example implementations, on in the local and one in the remote context.

The second half explores autonomic visualisation in the more general case. A simulation tool, created for the purpose of designing autonomic visualisation infrastructure is presented. This tool, SimEAC, provides a way of facilitating the development of techniques for managing large-scale visualisation systems.

The abstract design of the simulation system, as well as details of the implementation are presented. The architecture of the simulator is explored, and then the system is evaluated in a number of case studies indicating some of the ways in which it can be used. The simulator provides a framework for experimentation and rapid prototyping of large scale autonomic systems.

# Acknowledgements

First, I would like to thank Professor Min Chen for his patience and advice during his time as my supervisor while completing this PhD. I would also like to thank Professor Chuck Hansen for giving me the opportunity to vist the University of Utah in 2006.

Heartfelt thanks go to Beth Kupin, who helped keep me sane in the run up to submission deadlines for the papers that I wrote during the course of this PhD. Without her help, I would have found my PhD much more stressful.

I would also like to thank my parents for their support and advice over the years, especially for my mother for providing somewhere free of distractions where I could work while finishing this thesis.

Next, I need to thank Will Harwood, primarily for his coffee-making abilities, but also for his work on developing the official rules for the historic game of Labminton, without which the lab would have been a far less interesting place.

I would like to thank everyone in the Étoilé project for giving me some intersting problems to work on when I wanted to take a break from my thesis. Of particular note is Nicolas Roard, who persuaded me to stop complaining about the appaling state of desktop computing and do something about it and who helped turn nebulous ideas into ideas for working software.

I should probably thank Jo Gooch for providing various distractions when I was in need of a break, and ensuring that I rarely missed coffee time. Andy Gimblett and Basheera Khan have also been very helpful in this regard.

Finally, I need to thank all of the other inhabitants of the postgraduate lab, as well as many of the faculty of Computer Science, for making Swansea such an enjoyable place to study.

# Contents

| Ι | Int  | roduction                                                   | 1  |

|---|------|-------------------------------------------------------------|----|

| 1 | Aim  | s and Objectives                                            | 2  |

|   | 1.1  | Large Dataset Management                                    | 2  |

|   | 1.2  | System Simulation                                           | 4  |

|   | 1.3  | Summary of Aims                                             | 5  |

|   | 1.4  | Outline                                                     | 5  |

| 2 | The  | Problem of Visual Supercomputing                            | 7  |

|   | 2.1  | Introduction                                                | 7  |

|   | 2.2  | Visual Supercomputing                                       | 9  |

|   |      | 2.2.1 Definition                                            | 9  |

|   |      | 2.2.2 Semantic Contexts                                     | 10 |

|   |      | 2.2.3 Application Perspective                               | 11 |

|   |      | 2.2.4 User Perspective                                      | 12 |

|   |      | 2.2.5 System Perspective                                    | 12 |

|   | 2.3  | Trends in Visual Supercomputing                             | 13 |

|   |      | 2.3.1 The Dinosaurs                                         | 13 |

|   |      | 2.3.1.1 The Growth of Parallel Computation                  | 14 |

|   |      | 2.3.1.2 Sharing Data                                        | 16 |

|   |      | 2.3.1.3 Programming Models                                  | 17 |

|   |      | 2.3.1.4 Measuring Performance                               | 20 |

|   |      | 2.3.1.5 Parallel Visualisation                              | 21 |

|   |      | 2.3.2 Towards Local Visualisation                           | 23 |

|   |      | 2.3.3 Hardware for Visualisation                            | 24 |

|   | 2.4  | Applications of Visual Supercomputing                       | 26 |

|   |      | 2.4.1 Alternative Reality                                   | 26 |

|   |      | 2.4.2 Distributed Visualisation                             | 28 |

|   |      | 2.4.3 Visual Data Mining and Large-scale Data Visualisation | 29 |

|   |      | 2.4.4 Scientific Computation and Computational Steering     | 31 |

| 3 | Auto | onomic Computing and Visual Supercomputing                  | 36 |

| - | 3.1  |                                                             | 36 |

|   | 3.2  |                                                             | 39 |

|   | 3.3  | e-Viz                                                       | 43 |

| Π | M                          | anaging Large Datasets                        | 46 |  |  |

|---|----------------------------|-----------------------------------------------|----|--|--|

| 4 | Out-                       | of-Core Techniques                            | 47 |  |  |

|   | 4.1                        | Motivation                                    | 47 |  |  |

|   | 4.2                        | The Anatomy of an Out-of-Core Algorithm       | 49 |  |  |

|   | 4.3                        | A Taxonomy of Approaches                      | 50 |  |  |

|   | 4.4                        | Related Work                                  | 52 |  |  |

|   |                            | 4.4.1 Out-of-core                             | 53 |  |  |

|   |                            | 4.4.2 External Memory                         | 53 |  |  |

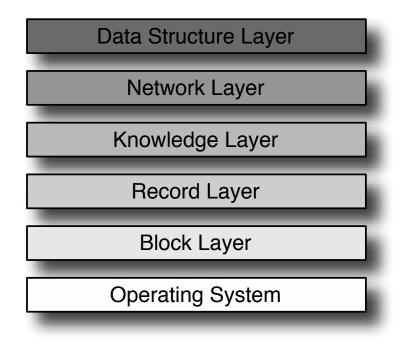

|   | 4.5                        | The 5-Layer Model                             | 54 |  |  |

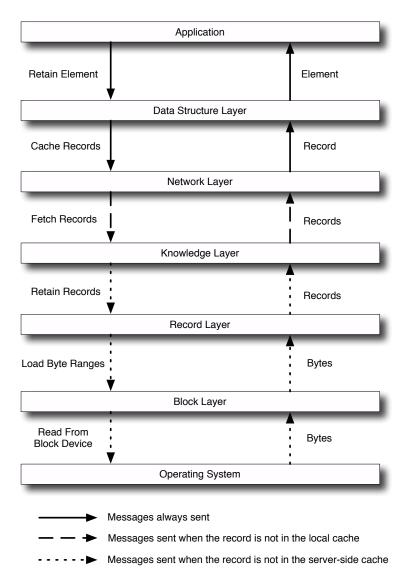

|   |                            | 4.5.1 The Block Layer                         | 55 |  |  |

|   |                            | 4.5.2 The Record Layer                        | 56 |  |  |

|   |                            | 4.5.3 Knowledge Layer                         | 56 |  |  |

|   |                            | 4.5.4 Network Layer                           | 57 |  |  |

|   |                            | 4.5.5 Data Structure Layer                    | 57 |  |  |

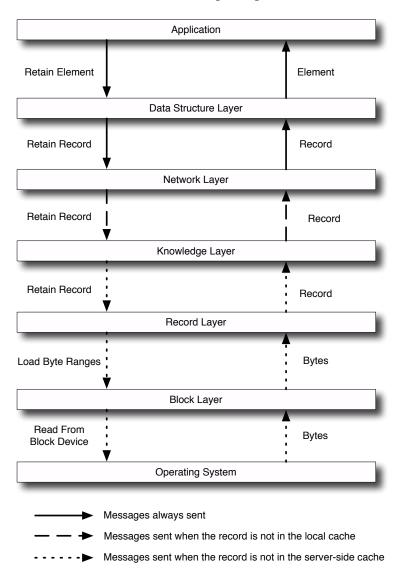

|   | 4.6                        | Interaction Between Layers                    | 58 |  |  |

|   |                            | 4.6.1 Retaining an Element                    | 59 |  |  |

|   |                            | 4.6.2 Predicting Usage                        | 61 |  |  |

|   | 4.7                        | Interface Specification for Layers            | 62 |  |  |

|   |                            | 4.7.1 Block Layer                             | 62 |  |  |

|   |                            | 4.7.2 Record Layer                            | 62 |  |  |

|   |                            | 4.7.3 Knowledge Layer                         | 63 |  |  |

|   |                            | 4.7.4 Network Layer                           | 64 |  |  |

|   |                            | 4.7.5 Data Structure Layer                    | 64 |  |  |

|   | 4.8                        | Reference Implementation                      | 65 |  |  |

|   |                            | 4.8.1 Local Implementation                    | 67 |  |  |

|   |                            | 4.8.1.1 Block Layer                           | 67 |  |  |

|   |                            | 4.8.1.2 Record Layer                          | 70 |  |  |

|   |                            | 4.8.1.3 Data Structure Layer                  | 72 |  |  |

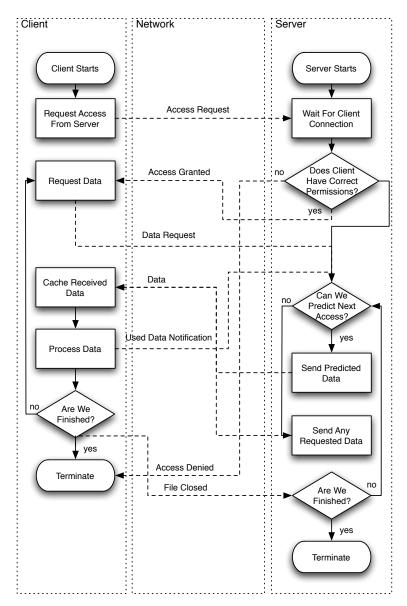

|   |                            | 4.8.2 Client-Server Implementation            | 73 |  |  |

|   |                            | 4.8.2.1 Message Types and Flow                | 73 |  |  |

|   |                            | 4.8.2.2 Message Detail                        | 74 |  |  |

|   |                            | 4.8.2.3 Cache File Layout                     | 76 |  |  |

|   |                            | 4.8.2.4 Client Interface                      | 77 |  |  |

|   |                            | 4.8.2.5 Agent Interface                       | 78 |  |  |

|   |                            | 4.8.2.6 Preliminary Results                   | 78 |  |  |

|   | 4.9                        | Conclusions                                   | 79 |  |  |

| 5 | Out-of-Core Sample Problem |                                               |    |  |  |

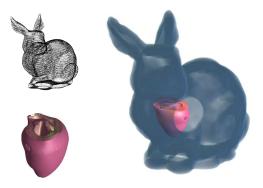

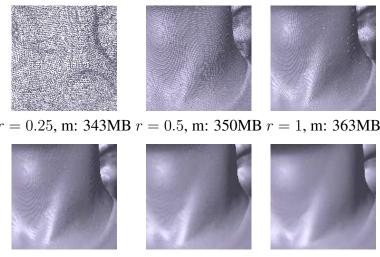

|   | 5.1                        | Introduction                                  | 81 |  |  |

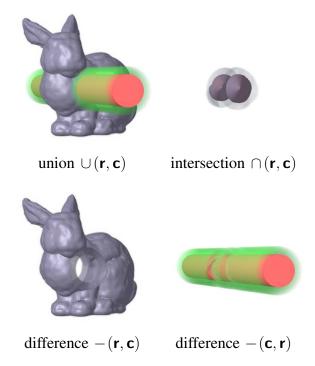

|   | 5.2                        | Modeling and Rendering Multiple Point Sets    | 83 |  |  |

|   |                            | 5.2.1 Point-based Volume Object (PBVO)        | 83 |  |  |

|   |                            | 5.2.2 Volume Scene Graphs                     | 84 |  |  |

|   |                            | 5.2.3 Discrete Ray Tracing                    | 85 |  |  |

|   |                            | 5.2.4 The Benefits and Costs of Using Octrees | 86 |  |  |

|   | 5.3                        | Out-of-core Rendering                         | 88 |  |  |

| 4          | <ul> <li>5.3.1 Algorithm Overview</li></ul>            | 92<br>95<br>97<br>98<br>98<br>98 |

|------------|--------------------------------------------------------|----------------------------------|

| 5          | 5.4.3         Performance                              |                                  |

| <b>6</b> A | Comparison of Algorithm and Knowledge Based Approaches | 104                              |

|            | .1 Introduction                                        |                                  |

|            | .2 A Knowledge-based Approach                          |                                  |

|            | .3 Algorithm Evaluation                                |                                  |

|            | .4 Conclusions and Future Work                         |                                  |

|            | .5 Detailed Results                                    |                                  |

|            |                                                        | 110                              |

| III        | Autonomic System Simulation                            | 128                              |

| <b>7</b> A | In Overview of SimEAC                                  | 129                              |

|            | .1 Introduction                                        |                                  |

|            | .2 Related Work                                        |                                  |

|            | .3 Motivation                                          |                                  |

|            |                                                        |                                  |

| _          | 7.3.1 Emergent Properties                              |                                  |

| /          |                                                        |                                  |

|            | 7.4.1 Hardware Simulation                              |                                  |

|            | 7.4.2 Resource Managers                                |                                  |

| _          | 7.4.3 Tasks                                            |                                  |

|            | .5 Simulating Failure                                  |                                  |

|            | .6 Simulation Engine                                   |                                  |

|            | 7.6.1 Messages                                         |                                  |

|            | 7.6.2 Time                                             |                                  |

|            | 7.6.3 Output                                           | 147                              |

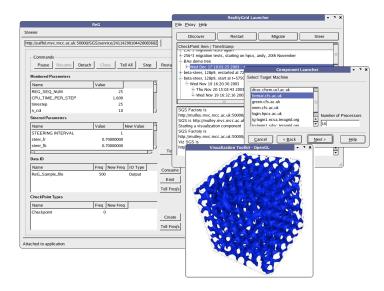

|            | imEAC Design and Use                                   | 148                              |

|            | .1 Introduction                                        |                                  |

| 8          | .2 Requirements and Implementation                     |                                  |

|            | 8.2.1 Abstract Operation                               |                                  |

|            | 8.2.2 Easy Re-Configuration                            | 149                              |

|            | 8.2.3 Support for Large Systems                        | 149                              |

|            | 8.2.4 Simple Development                               | 150                              |

|            | 8.2.5 Extensible Design                                | 150                              |

| 8          | .3 Application Programming Interfaces                  | 150                              |

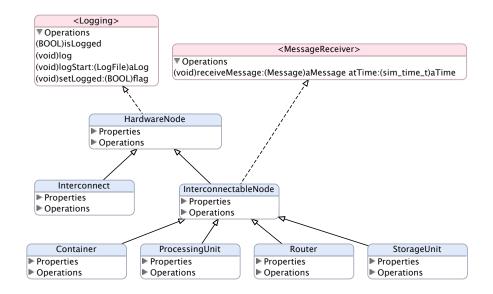

|            | 8.3.1 Hardware Simulation                              | 151                              |

|            | 8.3.2 Software Simulation                              | 153                              |

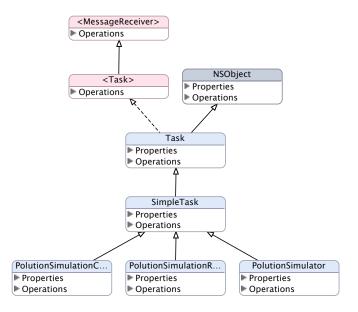

|         |                                         | 8.3.3                                                                                                        | Tasks                                                                                                       | 155                                                                                     |

|---------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|         |                                         |                                                                                                              | 8.3.3.1 Adding Tasks                                                                                        |                                                                                         |

|         |                                         | 8.3.4                                                                                                        | Creating New Resource Managers                                                                              | 159                                                                                     |

|         |                                         | 8.3.5                                                                                                        | Simulating Failure                                                                                          | 160                                                                                     |

|         |                                         | 8.3.6                                                                                                        | Output                                                                                                      |                                                                                         |

|         | 8.4                                     | SimEA                                                                                                        | C API Details                                                                                               | 161                                                                                     |

| 9       | Sim                                     | EAC Ca                                                                                                       | se Studies                                                                                                  | 165                                                                                     |

|         | 9.1                                     | Case St                                                                                                      | tudy: The "Organic Grid"                                                                                    | 166                                                                                     |

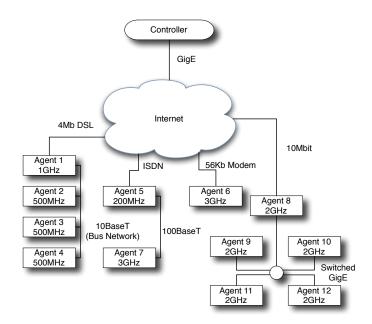

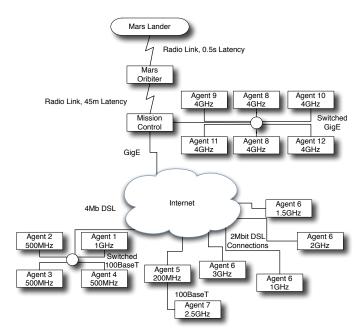

|         |                                         | 9.1.1                                                                                                        | Configurations                                                                                              |                                                                                         |

|         |                                         | 9.1.2                                                                                                        | Results                                                                                                     | 168                                                                                     |

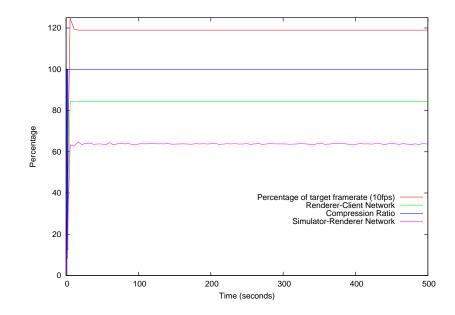

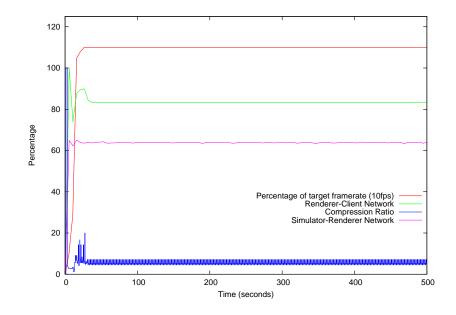

|         | 9.2                                     | Case St                                                                                                      | tudy: An Autonomic Visualization System                                                                     | 170                                                                                     |

|         |                                         | 9.2.1                                                                                                        | Simulated Tasks                                                                                             | 171                                                                                     |

|         |                                         | 9.2.2                                                                                                        | Resource Managers                                                                                           | 171                                                                                     |

|         |                                         | 9.2.3                                                                                                        | Hardware                                                                                                    | 171                                                                                     |

|         |                                         | 9.2.4                                                                                                        | Results                                                                                                     | 172                                                                                     |

|         | 9.3                                     | Summa                                                                                                        | ary and Conclusions                                                                                         | 175                                                                                     |

|         |                                         |                                                                                                              |                                                                                                             |                                                                                         |

| I       | / <b>C</b>                              | losing                                                                                                       | Remarks                                                                                                     | 177                                                                                     |

|         |                                         | losing                                                                                                       |                                                                                                             | 177<br>178                                                                              |

|         | Con                                     | clusions                                                                                                     |                                                                                                             | 178                                                                                     |

| 10      | <b>Con</b><br>10.1                      | clusions<br>Future                                                                                           | Work                                                                                                        | <b>178</b><br>180                                                                       |

|         | <b>Con</b><br>10.1                      | clusions                                                                                                     | Work                                                                                                        | 178                                                                                     |

| 10      | Con<br>10.1<br>Aj                       | clusions<br>Future V<br>opendic<br>SimEA(                                                                    | Work                                                                                                        | 178<br>180<br>182<br>183                                                                |

| 10<br>V | Con<br>10.1<br>Aj                       | clusions<br>Future V<br>opendic<br>SimEA(                                                                    | Work                                                                                                        | 178<br>180<br>182<br>183                                                                |

| 10<br>V | Con<br>10.1<br>A <sub>I</sub><br>The    | clusions<br>Future<br>Opendic<br>SimEAC<br>Loading                                                           | Work                                                                                                        | 178<br>180<br>182<br>183<br>183                                                         |

| 10<br>V | Con<br>10.1<br><b>A</b> I<br>The<br>A.1 | clusions<br>Future<br>Opendic<br>SimEAC<br>Loading                                                           | Work                                                                                                        | 178<br>180<br>182<br>183<br>183<br>183<br>184                                           |

| 10<br>V | Con<br>10.1<br><b>A</b> I<br>The<br>A.1 | clusions<br>Future<br>Opendic<br>SimEAC<br>Loading<br>User In<br>A.2.1                                       | Work                                                                                                        | 178<br>180<br>182<br>183<br>183<br>184<br>185                                           |

| 10<br>V | Con<br>10.1<br><b>A</b> I<br>The<br>A.1 | clusions<br>Future<br>Opendic<br>SimEAC<br>Loading<br>User In<br>A.2.1                                       | Work                                                                                                        | <b>178</b><br>180<br><b>182</b><br><b>183</b><br>183<br>183<br>184<br>185<br>185        |

| 10<br>V | Con<br>10.1<br><b>A</b> I<br>The<br>A.1 | clusions<br>Future V<br>opendic<br>SimEAC<br>Loading<br>User In<br>A.2.1<br>A.2.2                            | Work .   ces   C User Interface   g Bundles   .   iterface Overview   .   Containers   .   Processing Units | <b>178</b><br>180<br><b>182</b><br><b>183</b><br>183<br>183<br>184<br>185<br>185<br>186 |

| 10<br>V | Con<br>10.1<br><b>A</b> I<br>The<br>A.1 | clusions<br>Future V<br>opendic<br>SimEAC<br>Loading<br>User In<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5 | Work                                                                                                        | <b>178</b> 180 <b>182 183</b> 183 183 184 185 185 186 186 187                           |

| 10<br>V | Con<br>10.1<br><b>A</b> I<br>The<br>A.1 | clusions<br>Future V<br>opendic<br>SimEAC<br>Loading<br>User In<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5 | Work                                                                                                        | <b>178</b> 180 <b>182 183</b> 183 183 184 185 185 186 186 187                           |

Part I

Introduction

## **Chapter 1**

# **Aims and Objectives**

#### Contents

| 1.1 | Large Dataset Management | 2 |

|-----|--------------------------|---|

| 1.2 | System Simulation        | 4 |

| 1.3 | Summary of Aims          | 5 |

| 1.4 | Outline                  | 5 |

Visualisation applications continue to require more and more computational power. Scientific datasets are now measured in gigabytes or terabytes, and show no sign of slowing their growth. The process of extracting meaningful information from datasets of this size through the process of visualisation can be computationally very expensive.

Current approaches to visualisation tend to follow a somewhat ad-hoc approach to the problem of very large scale deployments. Existing algorithms are applied to new problems with some slight modifications for their new environment. Chapter 2 outlines the problems involved in deploying a large-scale visualisation infrastructure, and some attempts to address these problems.

The term Autonomic Computing was coined by IBM [144] to describe an evolution in management of complex systems. This thesis will describe a vision for applying this and related concepts to the problem of large scale visualisation, and will demonstrate the progress made in this endeavour.

Delivering a full autonomic environment for visualisation would be far beyond the scope of a single PhD thesis, and so two parts of the problem will be addressed directly.

### **1.1 Large Dataset Management**

The rapid growth of data from both complex simulations and high-resolution scanning instruments has outstripped the rate of growth of the physical memory, and in some cases

even local disk storage. This problem is exacerbated by the rise in mobile computing. A modern laptop has a significant amount of processing power [287, 213] - often including a relatively fast GPU - and so is up to the task of performing a number of forms of visualisation. In the coming years it appears likely that this trend will extend to handheld devices.

The growth in data size as well as the shrinking of the devices on which the data is likely to be displayed presents a range of problems when it comes to data management. Most operating systems provide some support for paged virtual memory. These typically work on two key assumptions:

- 1. The computer has almost enough physical memory, and should only spill over in to swap space occasionally.

- 2. The working environment is multitasking, and idle applications can be completely swapped out.

The first assumption comes from the fact that most applications have a relatively small *working set*, which changes infrequently. When this change occurs, it is mildly irritating to the user for their computer to pause briefly, but does not have a great deal of impact on overall performance.

Neither of these assumptions necessarily holds for a visualisation task. The dataset might be several times the size of RAM, and the rendering algorithm may need several passes over the entire dataset. This causes most operating systems to experience *thrashing*, the situation in which most of their time is spent swapping data between disk and RAM rather than performing useful computations.

One application for which this is a significant problem is *discrete ray tracing* of point sets. This application suffers from the fact that the access patterns through the data are highly dependent on the data itself, with the positions of both the points themselves and the light sources within the scene affecting the paths of the rays.

The discrete ray tracer application will be used as a test case for examining prefetching techniques. Since this application has serious memory usage problems, both in terms of size and access patterns, it makes an ideal study for evaluating pre-fetching strategies. The situation in which no pre-fetching occurs, demand paging, produces highly sub-optimal results, and it is anticipated that the addition of a more advanced data management strategy can provide significant performance benefits.

It should be possible to design such a strategy by first understanding the way in which the ray tracing algorithm works. While this is useful in and of itself, doing so does not require the use of autonomic concepts, nor is it likely to produce a solution that will be useful in other situations.

Such an algorithm could, however, be used as a base-line for evaluating other techniques. Of more use in the general case would be an algorithm that did not rely on understanding the nature of the rendering algorithm. This could, potentially, be adapted to other rendering techniques, eliminating the need for such things to be created on a per-problem basis. This thesis aims to evaluate the possibility of designing such an algorithm, and to compare the performance of a system-specific approach with an autonomic one.

### **1.2 System Simulation**

Designing a fully autonomic infrastructure for visualisation is a massive task, and building one presents an even greater challenge. One of the biggest problems of such an endeavour relates to the problems (and opportunities) associated with emergent properties.

Emergent properties arise when relatively simple systems are assembled to form complex ones. The complex systems exhibit behaviours that are not always apparent from the simple designs. In some cases, these can be highly advantageous, and can allow simple designs to be used in complex rôles. In others, they are problematic. If a systems is not designed with emergent properties in mind, then they can often cause pathological behaviour.

For this reason, it is necessary to test an autonomic infrastructure as early as possible in the design process and attempt to discover any emergent behaviours, then either take advantage of them or eliminate them. This, unfortunately, can not be done by techniques such as unit testing, since it requires the entire system to be tested simultaneously.

The proposed solution to this problem is simulation. A simulation environment matching the needs of autonomic computing would allow simplified models of individual components to have their interactions with other parts of the system tested, without the cost and effort of building the entire system.

This thesis aims to present a working system to address this need. Such a system must be easy to use and extend, and have the ability to work at varying levels of granularity. As a system is developed it will be possible to use prototypes and even final versions of components to provide more calibration data to the system. A good simulation environment must adapt to this growing amount of input data.

Scalability also extends in the other direction. It must also allow the user to perform highly detailed simulations of a subset of components, and more coarse simulations of the entire system distributed over a large grid.

Visualisation tasks are fairly similar to other tasks which could be performed by an autonomic grid environment, and so it is hoped that such a simulator would be usable for evaluating systems that were not directly tied to visualisation. To this end, it should not make any assumptions about the nature of visualisation tasks. This is important even within the context of visualisation, since such assumptions become outdated rapidly. Visualisation used to be solely the province of supercomputers, and later high-end workstations. Now a large number of visualisations can be performed on modest commodity hardware, and even hand-held computers often come with some form of graphics co-processor.

The gradual move from thin-, or dumb-client through desktop and laptop and to ubiquitous computing shows that assumptions about the location and distributions of workloads within a computational system rarely last. Autonomic computing is somewhat orthogonal to the underlying distribution paradigm, but is often identified closely with ubiquitous computing. A fully autonomic grid infrastructure would be most likely to exist within the overall context of ubiquitous computing, but deployment of some components would almost certainly begin before such a setting existed. For this reason, a simulator must be able to handle both existing and proposed systems, and to allow the gradual transition from one to the other to be effective.

The usability of such a system can only be evaluated experimentally, and so it is aimed that the simulation should be used for some real-world tasks and evaluated.

### **1.3 Summary of Aims**

The aims of this thesis can be summarised as follows:

- 1. Create an out-of-core prefetching strategy for the rendering problem outlined above.

- 2. Determine whether it is possible to achieve equivalent performance from a general, knowledge-based, prefetching algorithm.

- 3. Devise a systematic model for building out-of-core systems.

- 4. Demonstrate the model is feasible by providing at least one implementation of it.

- 5. Design a simulation system that can be used for developing an autonomic computing infrastructure.

- 6. Implement and evaluate the system.

If this thesis meets the goals outlined here then it will provide a demonstration of the effectiveness of knowledge-based solutions and provide a systematic means for other researches to incorporate these ideas into their own specific problems. It is hoped that these will be able to augment, and even replace, existing application-specific strategies. The later goals relate more generally to the field of autonomic visualisation and, if met, will facilitate the development of this very young field to a significant degree by allowing rapid evaluation of algorithms aimed at this field.

### 1.4 Outline

The remainder of Part I describes the problem associated with visual supercomputing in general, and suggests how autonomic computing could be applied to give some possible solutions. The remainder of the thesis will then focus on some areas within this topic.

Part II describes the problem of managing large datasets, specifically those too big to fit in RAM and those too big to be stored locally. These are increasingly common in

visualisation. Modern scientific instruments can generate data of a size limited only by the size of the disk arrays used to store them.

This part will describe a visualisation system for large data sets and a pre-fetching strategy tied to the renderer. It will then show how a self-optimising approach can be used to simplify the development of systems to handle them. An adaptive approach to data pre-fetching is proposed, as well as a systematic model for building out-of-core systems. Two example implementations of the model are discussed.

Part III describes a system for simulating the interactions between components running on a heterogeneous grid environment. This system was developed to aid the development of autonomic distributed visualisation systems, and some example uses are discussed.

## Chapter 2

## The Problem of Visual Supercomputing

#### Contents

| 2.1 | Introduction                          | 7  |

|-----|---------------------------------------|----|

| 2.2 | Visual Supercomputing                 | 9  |

| 2.3 | Trends in Visual Supercomputing       | 13 |

| 2.4 | Applications of Visual Supercomputing | 26 |

### 2.1 Introduction

Today there is a variety of computational resources available to visualisation. While a huge number of users are contented with the visualisation capabilities provided through modern desktop computers and powerful 3D graphics accelerators, many are still relying on high performance computing facilities to visualize very large data sets or to achieve real-time performance in rendering a complex visualisation. In some areas, users have already demanded visualisation capabilities to be provided through mobile computing systems, such as PDAs (Personal Digital Assistants), most of which are yet to benefit from powerful 3D graphics accelerators. As the size of visualisation data (e.g., in visual data mining), the complexity of visualisation algorithms (e.g., for virtual environments) continues to grow, it is unlikely that visualisation users can be served adequately, at least in the coming years, by an infrastructure largely based on desktop computers.

This leads to a series of questions:

- What would be an adequate infrastructure?

- In what way do the computational requirements of visualisation differ from other software technologies?

- Is it desirable or feasible to bring a range of technologies under one management (not necessarily under one roof)?

- If it were feasible to build such an infrastructure, what would be an appropriate virtual machine interface for the infrastructure?

In fact, the computer graphics and visualisation community has been seeking answers for these questions for the past few decades. The community has invested a huge amount of effort in developing specialized graphics hardware, has always been among the first to deploy the latest technologies for high performance computing, and has accumulated large volumes of research outputs in parallel, distributed, and web-based techniques for visualisation. Recently, the community has shown equally great enthusiasm to embrace the cluster, Grid and mobile technologies. However, in general, the community tended to address these questions mainly from the perspective of visualisation technology in isolation, rather than from the perspective of a coherent infrastructure design.

In this chapter, the historic route for deploying new technology in the context of visualisation is examined and a broad range of scientific and technological developments, including theories, algorithms, hardware, software and services, are described. The term *Visual Supercomputing* is used to encompass the concepts and technologies required to build a computing infrastructure for visualisation. An overview of the state of the art of technologies in hardware and software for visualisation are presented, and the impacts of the Internet, Grid and mobile technologies is discussed.

Those latest developments that are relevant, or potentially relevant, to visualisation infrastructure are highlighted. A set of technical challenges in realising a visual supercomputing infrastructure that manages visualisation tasks in complex networked computing environments, as well as manages users experience in accessing and interacting with visualisation resources are proposed. Later chapters in this thesis discuss the application of principles from the field of *autonomic computing* to the solution of some of the challenges presented.

There is now a growing body of experience in adapting applications to a Grid environment. What is emerging is a consensus that the original idea of a computational Grid that behaved like a utility Grid for computation is perhaps oversimplified. There may be several different structures for Grids depending on whether the resources aggregated in the Grid are to serve large-scale computation, large-scale data handling, complex data sources (e.g., bioinformatics databases) or perhaps to integrate business processes. In this, the visual supercomputing paradigm presents novel challenges to the Grid concept. A number of pioneering projects, described in this chapter, have been testing the implications of a Grid for various visualisation applications and have raised many technical issues including real-time processing, synchronisation of resource allocation and interaction between clients and Grid services.

This chapter is organized into the following sections. In Section 2.2, the term *Visual Supercomputing* is defined. In Section 2.3, major scientific and technological developments are reviewed by following the arrivals of different computing technologies, identify the state of the art technologies are identified that have are required for building an infras-

tructure for visual supercomputing. In Section 2.4, a collection of applications that would benefit enormously from such an infrastructure are examined, and their technical requirements discussed.

### 2.2 Visual Supercomputing

In this section, the term 'Visual Supercomputing' is defined. Its relevance to the three semantic contexts of visualisation is examined. Finally, the technical scope of visual supercomputing from the perspectives of *applications*, *users* and *systems* respectively.

#### 2.2.1 Definition

**Definition 2.1** (Visual supercomputing). Visual supercomputing is concerned with the infrastructural technology for supporting visual and interactive computing in general, and visualisation in particular, in complex networked computing environments.

This thesis is focussed on the subject domain of visualisation, although most of the discussion in this chapter can be extrapolated to other subject domains involving visual and interactive computing, such as computer-aided design, computer animation, and computer vision.

As an *infrastructural technology*, visual supercomputing encompasses a large collection of hardware technologies and software systems for supporting the computation and management of visualisation tasks. It focuses on generic technologies for managing the specification, execution and delivery of visualisation tasks. It addresses issues such the scheduling of visualisation tasks, hardware and software configurations, parallel and distributed computation, data distribution, communications between different visualisation tasks, and communications between visualisation tasks and their couplings such as computation tasks or data collection tasks. In addition, it provides infrastructural support to users' interaction with visualisation resources. Nevertheless, visual supercomputing does not concern a specific algorithm and technique for processing a specific type of data in order to generate visualisation results.

Explicit emphasis is given to complex networked computing environments, as this chapter is not intended as only a survey of the technologies that have been developed so far in the context of visual supercomputing, but as a report on technologies that are in place as well as that are desirable for a future infrastructure. No doubt such an infrastructure must take *web computing*, *Grid computing* and *mobile computing* into account. Hence it has to provide comprehensive support to visualisation tasks in complex heterogeneous networked computing environments. As current trends in hardware design are increasingly driven by power consumption as well as raw speed, there is an increasing reliance on dedicated hardware. This trend makes it appear likely that heterogeneous environments will be the norm, rather than the exception, in the near future. The visual supercomputing environment is best considered as a global Grid infrastructure for visualisation. The above-mentioned technical features of visual supercomputing have clearly set it apart from the traditional subject domains such as *hardware architectures for visualisation, parallel and distributed computation for visualisation, web-based visu-alisation,* and *collaborative visualisation*. While the advances in these traditional subject domains will have significant influence in shaping the infrastructure of visual supercomputing, building such an environment will require not only integrating these technical advances together in an environment, but also bringing in, and developing new, technologies for significantly improving the quality of services (QoS) of such an infrastructure and users' experience.

#### 2.2.2 Semantic Contexts

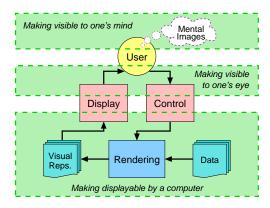

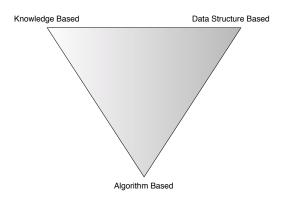

The term 'visualising' refers to a process that extracts meaningful information from data, and constructs a visual representation of the information. In the field of visualisation, this *process* is commonly considered in three different but interrelated semantic contexts as illustrated in Figure 2.1.

Figure 2.1: Three semantic contexts of visualisation.

- Making displayable by a computer. This is concerned with the algorithmic and computational process of extracting information and rendering a visual representation of the information. In this semantic context, a visual supercomputing infrastructure should address issues such as allocating and scheduling computational resources for visualisation tasks, managing data distribution, and providing mechanisms for inter-process, and inter-task communications within an infrastructure.

- **Making visible to one's eyes.** This is concerned with the process of specifying meaningful information, designing appropriate visual representations, and conveying visual representations to viewers. In this semantic context, a visual supercomputing infrastructure should address issues related to the interaction between users and their visualisation tasks, which can be conducted in a variety of forms, including interactive virtual environments, Internet-based collaborative environments, mobile visualisation environments, and so on.

Making visible to one's mind. This is concerned with users' thought process and cognitive experience of interpreting received information (not necessarily in a visual form) in one's mind and converting the information to knowledge in pictorial representations. In this semantic context, it is neither desirable nor perhaps feasible for a visual supercomputing infrastructure to manage the thought process of a user.

This section presents further detailed discussions on how visual computing relates to the above three semantic contexts, and provides rationalisation for focusing infrastructural support on the processes of *making displayable by a computer* and *making visible to one's eye*, with the state of the art technologies in visual supercomputing. It also argues for the necessity for introducing gradually new capabilities in a visual supercomputing environment, to support the process of *making visible to one's mind*.

#### 2.2.3 Application Perspective

The demands for visualisation multiply in every direction, and there is an increasing number of new applications, resulting in new, and sometimes conflicting, requirements. For example:

- In some applications (e.g., bioinformatics), the size of datasets to be processed continues to grow, while in others (e.g., mobile visualisation), a careful control of data size is absolutely necessary. Even in cases where the data is sufficiently small to fit on a single machine, collaboration and security concerns may make it advisable to store it centrally. This makes the ability to quickly access the required subset of data that is available.

- In many applications (e.g., those involving 3D virtual environments), users still have plenty of appetite for photorealistic visualisation at an interactive speed, while in others (e.g., visual data mining), schematic visual representations and non-photo-realistically rendered images are often able to convey more information. A visual supercomputing environment must be able to handle both latency- and throughput-dependent tasks.

- In many applications (e.g., virtual endoscopy), interactive visualisation can now be achieved with modern personal computers, hence small integrated systems provide a high degree of independence to users who operate in various practical situations. Meanwhile, other applications (e.g., those centralized around one or more data warehouses) require a substantial amount of computation for visualisation to be closely coupled with the source of data. Some applications, which have distributed data sources or dynamic data sources, demand a more complex computational model. A visual supercomputing environment must scale to all devices from hand-held machines up to supercomputers.

From the perspective of applications, an important requirement for a visual supercomputing infrastructure is choice. It has to provide support for a large collection of platforms, methods, mechanisms and tools to serve different categories of application, as well as offer each individual application a diverse selection of means to accomplish a visualisation task.

Section 2.4 considers several major applications, which collectively characterize the main requirements for a visual supercomputing infrastructure.

### 2.2.4 User Perspective

Visualisation users are no longer limited to scientists and engineers. At the same time, a visualisation process often requires a high degree of domain knowledge about the application concerned. While the diversity of applications demands a visual supercomputing environment to provide a large collection of platforms, methods, mechanisms and tools, users require the service to be tailored to individual needs, and to be delivered in a seamless manner. Many users, especially those less technically oriented, would very much hope for a secretary-like visualisation service, where they simply submit the data, give instructions and receive results. Although to get appropriate results may require a few feedback loops, many users certainly do not wish to get involved in choosing hardware, programming parallelism, organizing storage for input and output data, and so on. Further more, like a secretary, perhaps a visual supercomputing infrastructure should accumulate knowledge about various entities in the environments, profiling hardware capabilities, software usage, users' preference, etc. and gradually improving its quality of services to individual users.

Recent developments in business computing, such as electronic customer relationship management (e-CRM) [241, 183], has shown that it is possible to provide users with better quality of services with appropriate technologies that are capable of collecting and processing users' experience. The emergence of *autonomic computing* [165] is gathering further momentum in developing self-managed services in a complex infrastructure (see also Section 3.2). Therefore a visual supercomputing infrastructure should have the responsibility for managing:

- visualisation resources,

- visualisation processes,

- source data and resultant data,

- users' interaction and communication,

- users' experience in accomplishing a visualisation tasks.

### 2.2.5 System Perspective

From the system perspective, a visualisation task is a kind of computation task, which exhibits a specific class of characteristics. The infrastructure of visual supercomputing is built upon a range of underlying technologies, including computer hardware, operating systems, programming languages, data warehouses, communications, world-wide-web, Grid computing and knowledge-based systems. It is neither sensible nor feasible for the

visualisation community to attempt to provide solutions in all these aspects. However, it is necessary for the construction of such an infrastructure to bring in the latest advances in other fields of computing and communications, and moreover, to influence the developments in these fields.

The following section, examines in detail the major advances and the state of the art in the relevant fields.

### 2.3 Trends in Visual Supercomputing

Visualisation is fundamentally an application of computing, and so trends in visual computing tend to follow overall trends in computing. The predominant trend in the industry since its inception has been towards miniaturisation. The one prediction that has always held in every aspect of computing has been 'you will be able to do this with a smaller machine next year.'

This section will provide a description of some of the more important trends and milestones in the computing industry, and their impact on visualisation. As visualisation is such a computationally-demanding application, it has always been near the forefront of uses for new advances.

For more information, please see the relevant surveys [332, 135, 27, 321, 104, 161, 40] and some major publications [94, 304, 127] [331, 281, 171].

### 2.3.1 The Dinosaurs

The pre-history of computing is dominated by large machines taking several rooms worth of space. The Cray-1 was possibly the first supercomputer deserving the name, although its computational power was small by modern standards. Visualisation was not the only task performed on this model, but Elwald and Mass's vector graphics library for this platform [103] represents some of the first efforts at directing supercomputing power towards visualisation.

Once the potential for computer visualisation began to be understood by the scientific community at large, the field began to get more attention. Supercomputers are difficult to define, as a breed. Some personal computers have been advertised as 'supercomputers' based solely on US export restrictions on processing power during the tail end of the cold war. This metric is not particularly meaningful, since the PDAs of one age are the supercomputers of an earlier one. Most supercomputers are based around the idea of massively parallel computational engines with very fast interconnects between them. This broad scope will be used for the remainder of this section, which will thus include some techniques that post-date the widespread use of supercomputers for visualisation, but inherit some concepts from this age.

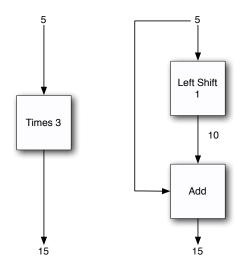

Figure 2.2: The decomposition of a multiply-by-three operation using functional parallelism.

#### 2.3.1.1 The Growth of Parallel Computation

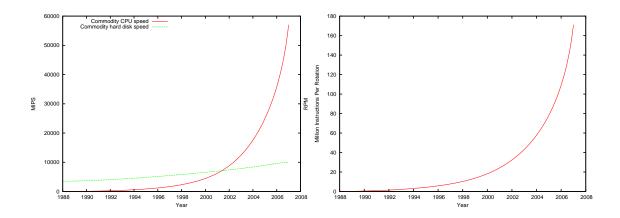

Computers are never quite fast enough. In 1965, Gordon Moore noted the trend that the number of elements that can be placed on an integrated circuit, for a fixed investment, doubles roughly every 18 months. This observation came to be known as Moore's Law [221].

Although Moore's Law says nothing about computational power, it has been a fairly accurate rule-of-thumb. If you double the number of transistors on a die, you can double the number of execution units, the amount of cache, etc. This is usually accomplished by a reduction in feature size, which comes with a corresponding increase in feasible clock speeds.

In spite of these gains, a single CPU is often still not fast enough. Or, more accurately, the cost of building a single CPU that is fast enough is prohibitive. A much cheaper alternative is to by two (or more) CPUs and join them together.

Most traditional programming models owe their heritage to very simple computers, and so have no concept of parallelism. New models were required, and two emerged. These were *functional parallelism* and *data parallelism*.

Functional parallelism, also called pipelining, describes a model by which an operation is split up into a number of stages, each of which can be executed sequentially. Figure 2.2 shows a trivial example, in which the function  $f(n) = n \times 3$  is decomposed into functionally parallel stages. Assuming that each block in the diagram can be executed on a separate execution unit, the right hand pipeline could run twice as fast as the left. This is exploited by modern CPUs at the instruction level, but in visualisation it is commonly done at a much coarse granularity giving rise to the term *visualisation pipeline*.

Data parallelism is conceptually simpler, but often harder to implement in practice. Data parallelism splits the data, rather than the algorithm. A data parallel version of the

multiply-by-three example would simply add a second multiplier. You could then achieve double the throughput, assuming that you could keep both supplied with data. The difficulty in implementing data parallelism comes from the fact that, for many applications, the data is not independent. Most modern hardware incorporates some form of data parallelism, from superscalar architectures in general purpose CPUs to multiple independent pipelines in GPUs.

In graphics, data parallelism is typically achieved using either *image space* or *object space* decomposition. Image space decomposition splits the workload up based on the pixels in the final image. Ray tracing is particularly suited to this approach, since each pixel in a ray-traced image is generated by a different ray, which is independent from the others. In rasterisation-based approaches, techniques such as *scan line interleaving* are common. In general, image space decomposition works better on *shared memory* architectures, since each thread needs access to all (or a large subset) of the source data for most techniques.

A final form of parallelism, known as *farm parallelism* is a hybrid of the two. In this, a problem is decomposed into computational tasks, encapsulating both a portion of data and some functional workload. These are typically independent, are are processed by whichever computational resources become free first. This form of parallelism is used by visualisation algorithms such as [242].

In terms of implementations, Flynn's taxonomy [111] still works well to describe the possible forms of parallel hardware in terms of the number of concurrent data and instruction streams. The simplest case, *single instruction, single data (SISD)* refers to the absence of any parallelism. At the other extreme, *multiple instruction, multiple data (MIMD)* refers to independent instructions working on multiple data streams, as is the case with independent processors. In the middle are *single instruction, multiple data*, (*SIMD*) and *multiple instruction, single data (MISD)* systems. The first, also known as vector processors, are common in supercomputer chips and increasingly as extra instructions on general purpose CPUs.

SIMD machines allow individual instructions to operate on vector rather than scalar quantities. While an add instruction in a SISD machine would be defined as  $add(x, y) \rightarrow x+y$ , the equivalent SIMD instruction might be defined as  $add((x_1, x_2, x_3, x_4), (y_1, y_2, y_3, y_4)) \rightarrow$  $(x_1 + y_1, x_2 + y_2, x_3 + y_3, x_4 + y_4)$ . Vector processors typically have a very large peak throughput, however it is difficult to keep them saturated. In the four-way vector example, adding two numbers together would take as long as adding four pairs of numbers together. Visualisation algorithms tend to be well suited to this kind of architecture, since a vector can be used to store each colour component (for example), and acted on independently.

The final approach, MISD, is perhaps the hardest to pin down. It is difficult to define a MISD machine, because most machines could be categorised as MISD. A multiply instruction could be considered to be a series of add and shift instructions, for example (and a shift instruction, itself, could be considered a series of add instructions). Very few machines, if any, have instructions so simple that they can not be considered to be combinations of simpler operations.

#### 2.3.1.2 Sharing Data

The simplest form of parallel computation is two completely independent computers, running two independent tasks. This could be regarded as the most widely-deployed form of parallel computation, since every computer in the world, past and present, is part of a grid implementing this form of parallelism. It is not usually regarded as a model of parallel computation, however. Some form of communication between computational resources is typically regarded as the basic entry requirement for being classed as a parallel computer.

There are two main ways of sharing data between a pair of processors; *shared memory* and *message passing*. The *Parallel Random Access Machine (PRAM)* model [112] represents the first method. PRAM describes a MIMD architecture with a number of independent processors with a shared clock and an unbounded memory space; the MIMD equivalent of an *unlimited register machine*. PRAM architectures can be categorised according to the capability of the memory; whether each location can be read from or written to concurrently. In modern machines, most RAM has no capability for concurrency, although specialised *Video RAM (VRAM)* has been designed to allow the DAC connected to the screen to read its contents while the CPU updated the contents, removing the need to lock the memory as the display was scanned. This has gone out of fashion in recent years as RAM prices have dropped enough to make double buffering the norm.

More recent models for parallel architectures have focussed on the layout of the memory, describing architectures according to whether access to the memory has a uniform cost [280, 50]. Uniform Memory Architecture (UMA) machines are those for which it does. UMA designs are typically found in systems which do not exhibit a large degree of parallelism<sup>1</sup>. The reason for this is that maintaining a uniform access cost for large numbers of processors to large amounts of memory requires either  $n \times m$  interconnects, where n is the number of processors and m is the number of banks of memory, or a large constant cost. UMA systems where the processing units are heterogeneous are referred to as symmetric multiprocessing (SMP) systems, since a task can run as easily on any processing unit. Volume visualisation often relies on memory systems supplying conflict-free simultaneous access to multiple voxel values in a volume dataset [255].

*Non-uniform memory architecture (NUMA)* systems exhibit greater scalability [345]. In a NUMA architecture, there is some fast, local, memory for each processing resource. The speed of access to this memory is constant, irrespective of the number of nodes in the system. In contrast, adding one node to a UMA system either increases the cost of memory access to all nodes, or increases the cost of building the system (often by a large amount). The largest disadvantage of a NUMA system is that it requires locality of reference to be used effectively, delegating data distribution to the programmer. This makes NUMA machines more of a challenge to effectively utilise.

The other model for sharing data is *message passing*. A message passing system partitions the address space so that each processor has its own private memory and explicitly sends and receives data from others. While these two models seem different, it is important to

<sup>&</sup>lt;sup>1</sup>What constitutes a 'large degree' depends largely on the year in which the system was designed.

note that it is relatively easy to implement one using the other. Shared memory can have message queues stored in it, and accesses to remote memory regions can be trapped and fetched using a message passing mechanism. It is important to distinguish between the underlying mechanism, and that exposed to the programmer.

A *distributed memory* system is one in which each processor has its own private memory, which is fast and not shared. A message passing mechanism is then used for non-local access. The Cray T3D is an archetypal example of this. A more modern implementation of this idea is found in the Cell microprocessor where each *synergistic processing unit* (*SPU*), of which there are eight on each die, has 256KB of very fast local memory and uses DMA transfers to access the system's main memory. A similar low-level design is used on most modern processors, although the fast local memory is not directly accessibly by the programmer; instead it is used as *cache* for the main memory, and the contents are determined at run-time by the cache controller. Distributed memory systems are often regarded as difficult to program, since they do not map to conventional programming languages very easily. CSP-based languages, such as Erlang [23] and Termite [123], are well suited to targeting these architectures, since their semantics more closely match the underlying hardware. In spite of this, distributed memory systems are popular for very high-end systems due to their ability to scale to many thousands of processors [299]. Distributed memory systems can have their nodes arranged in a variety of configurations.

Most UMA systems are *shared memory* systems at the low level. These typically make use of a distributed memory hierarchy, where each processor has a local cache that is not accessible to others. Maintaining coherence between these caches requires a *cache coherence protocol*. In the absence of cache coherence, a modification to a shared memory region might not be detected by one of the processors [299]. Some NUMA architectures also implement a cache coherency protocol. These are referred to as *cache coherent NUMA (ccNUMA)*. The one of the most widespread ccNUMA architectures currently is AMD's Opteron, where each CPU has a memory controller and communicates with the others over a message-passing point-to-point HyperTransport interconnect. When a memory location is updated, the cache lines containing it in all of the connected processors are flushed. This is a good example of the importance of distinguishing between the implementation and the programmer-visible design, since most operating systems expose Opteron machines as UMA systems to the programmer.

#### 2.3.1.3 Programming Models

Conceptually, the simplest model for programming parallel systems is shared memory, where each thread of execution has access to the same memory resources. While this is conceptually simple, it has several limitations. The most obvious is that it places a significant burden on the programmer, in terms of synchronisation. The second is that is is not ideal for NUMA systems. A shared memory system, where communication latencies are significantly under 1ms can present a shared memory view to a programmer using a structure such as a *dynamic interconnection network* [297] or a *crossbar switch* such as that found on the Cray Y-MP to keep latencies relatively constant. On NUMA

systems, however, the cost of accessing memory can vary widely. This makes reasoning about performance very difficult [121].

Shared memory does not have to be exposed as an untyped melange of data. Linda [55] is a coordination system, which exposes a *shared tuple space* to developers. Linda supports C and Fortran. A similar model is available for Java in the form of JavaSpaces. The SR language [16] supports both shared-address-space paradigm and messaging passing paradigm.

Message passing as a programming model scales better than pure shared memory, and maps more cleanly to the underlying mechanisms of NUMA systems. Some languages, such as Erlang and Termite, have been designed around this model, but they require significant changes to the design of many existing algorithms. These languages are based on the *communicating sequential processes* formalism, where a problem is decomposed into independent parts, with no shared resources, that communicate by passing messages.

Message passing mechanisms have been attached to other languages at the library level. The most popular for high-performance visualisation, and computing in general, is *Message Passing Interface (MPI)* [51]. This specification has been implemented for a variety of languages, including C/C++ and Fortran.

An alternative is the *Parallel Virtual Machine (PVM)*, from Oak Ridge National Laboratories. This uses an abstract virtual machine as the target, and an emulator for this machine. Although this incurs some performance penalty, it provides good fault tollerance and recovery, and so remains relatively popular [122]. A similar approach is taken by a derivative of the Plan 9 operating system, *Inferno*<sup>TM</sup> [99]. Inferno<sup>TM</sup> runs both as an operating system and in 'hosted mode' as a process in other operating systems, and is designed to run distributed applications written in the *Limbo* programming language and just-in-time compiled for the native platform.

In the late 1970s, Alan Kay proposed a method of software development where programs would be described as running on 'simple computers that communicate by message passing.' He termed this model *object oriented programming*. At the time, most computers had a single CPU and so the most efficient method for implementing message passing was synchronously, atop function calls. Languages such as Smalltalk built on this principle, however, present message passing as an abstraction and so allow different approaches to be used. Messages in Smalltalk-like languages can easily be replaced with trampolines which return a proxy object, which then blocks on access, implicitly extracting parallelism from synchronous algorithms<sup>2</sup>.

Other languages, such as Java and C++ adopt some aspects of object orientation, and replace function calls with method invocations as the basic primitive for controlling program flow. Function calls and method invocations are very similar, both in implementation and use. A method invocation in these languages is basically a function call scoped to an instantiation of an abstract data type; a verb to the object's noun.

<sup>&</sup>lt;sup>2</sup>An implementation of this idea in Objective-C by the author of this thesis is available from http://etoileproject.org

Function calls and method invocations are, at the local level, synchronous. Both have been extended to support parallel computation, however. Function calls have been extended as *remote procedure calls (RPC)*. A number of implementations of these exist, with the most common being those of Sun and Microsoft. While the procedure calls themselves complete synchronously, it is common for them to be used to initiate a longer process which then completes asynchronously.

The concept of RPC was extended by NeXT Computers to give *Portable Distributed Objects (PDO)*. The PDO system allowed both synchronous and asynchronous method calls to objects on remote machines. Since objects were passed as parameters, this gave more functionality than procedure calls. PDO was limited by the fact that it primarily worked on compiled languages, however which forced the classes to be distributed out-of-band before the system started.

The Java implementation, *remote method invocation (RMI)* overcame this limitation. Java classes are compiled as bytecode, which is machine-agnostic. This means that objects can be passed as parameters irrespective of whether their underling code had been distributed before hand. If they had not, then the bytecode could be distributed between nodes in the network and run.

Two PDO-like systems gained widespread adoption. The *Common Object Request Broker Architecture (CORBA)* [25] is a specification for method invocations across language and process boundaries. Microsoft's *Distributed Common Object Model (DCOM)* goes a step further, and specifies a binary interface, allowing DCOM objects to interact independently of the *object resource broker* on which they are running (although, in practice, the only DCOM implementation that has seen any widespread use is Microsoft's own). CORBA and COM, like PDO, use the object as the 'atom' — the unsplitable component — in the system. Globe [313] goes a step further, and permits a single object to be distributed amongst nodes.

In recent years, there has been a growth in distributed middleware, including coordinationbased systems such as Jini [240], and document-based designs such as Globus [114]. Many of these use XML at the protocol level [43], especially those based on web, and later grid-service architectures.

The idea of *dataflow computation* [275, 276] is an alternate model for parallel programming, in which execution is driven by the dependencies within the data. The Polytypic Grid [100] provides a similar model, making use of the implicit parallelism that can be extracted from functional languages (moving from  $\lambda$ -calculus to  $\pi$ -calculus for the underlying formalism) in combination with lazy evaluation to perform on-demand execution of a parallel graphics pipeline.

Dataflow computation has seen a lot of use in the context of visualisation, as it maps well to the visualisation pipeline abstraction. Implementations including OpenDX [2], AVS [311], IRIS Explorer [117], SCIRun [243] and DDV [222] are all examples of dataflow environments aimed at visualisation. They treat the visualisation pipeline as a directed graph, where each node represents a computation. This provides support for dataflow parallelism [285], since each node can be executed in parallel. There are some

limitations to most implementations of this approach, such as the inability to handle partial datasets [6], although this is a practical, rather than theoretical, limitation to the model.

One final model, that of *stream-based computation* provides an approach similar to data parallelism, but with some aspects of control parallelism. A stream-parallel system is composed of stream processing units, which take streams of commands and data and execute in parallel. This model is used by Chromium [149], which processes streams of OpenGL commands (which can be control or data, but are more often data). A set of extensions to VTK based on Chromium have also been proposed [223].

#### 2.3.1.4 Measuring Performance

The main reason for moving to parallel computation is to achieve better performance, and so it is important to be able to measure the increase on performance derived from the addition of extra processing units.

One of the most popular metrics is *speedup* [154]. This measures the increase in speed per added processing resource. Speedup is calculated as the ratio of the serial and parallel runtimes, multiplied by the number of processors. In the parallel case, the total time of all processors is taken, so a task which takes two seconds on each of two processors would have a parallel run time of four seconds. In the ideal case, the speedup for an algorithm will be the number of processors (P). Note that in many cases speedup is a function of P, rather than a constant. Some algorithms have a 'natural' degree of parallelism, and have a speedup of the order of P up to this value, after which little benefit is gained from adding more processors. In theory, the speedup can not exceed P, however in practice, concurrent applications may incur some overhead from context switching on a single processor that is removed when they are run on more. This is often apparent on highlyconcurrent applications written in languages such as Erlang. The upper bound on speedup is given by Amdahl's Law [12]. Given a problem of size w that has a sequential fraction of size  $w_s$  and a parallel fraction of size  $w_p = w - w_s$ , the upper bound of speedup is  $w/w_s$ , regardless the number of processors.

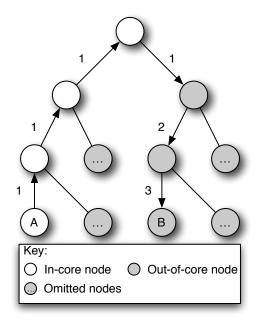

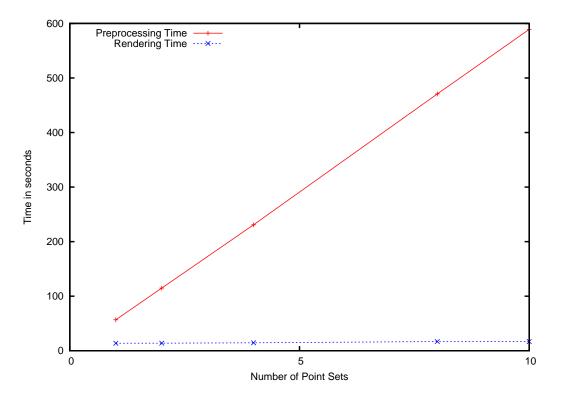

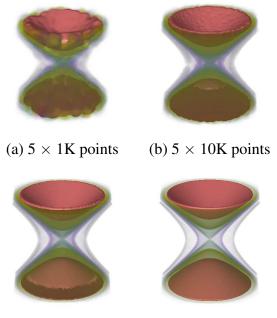

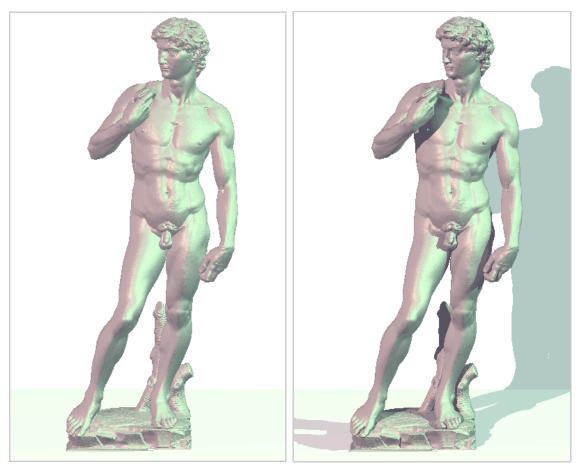

It is important to track the efficiency of a parallel approach. The *efficiency* of parallelisation is defined as the speedup divided by the number of processors. In the ideal case, the efficiency will approach 1. In general (for most non-trivial algorithms), it tends towards 0 as P tends towards infinity. At some point, it ceases to be economical to keep adding processors to a problem. Another way of determining this is the *cost* metric. This is the total computation time needed (the run time multiplied by the number of processors). If the speedup is less than P (i.e. the efficiency is less than one) then the cost will grow as P grows.